# A Review on Different Multilevel Inverters with Reduced Number of Switches to be used for AC Motor Drives

Akhilesh Kumar Yadav<sup>1</sup> and Ashavani Kumar<sup>2</sup>

<sup>1,2</sup>Physics Department NIT Kurukshetra Kurukshetra, India-136119 E-mail: <sup>1</sup>akhileshy6603@gmail.com, <sup>2</sup>ashavani@yahoo.com

**Abstract**—Multilevel inverters are playing an important role on today's time .This gives us good quality voltage performance, reduction of total harmonic distortion, reduces switching power loss and also give us high power ratings .The various types of topology that is made takes less power, voltage switching and voltage sources than the conventional topology. In this paper, we will discuss several types of topologies, modulation techniques and how to reduce total harmonic distortion, switching losses and voltage stress. At the last we will conclude topology review and their merits and demerits.

**Keywords**: Cascaded H-bridge (CHB), multilevel inverters (MLI), Total harmonic distortion (THD).

#### 1. INTRODUCTION

The multilevel inverters are a device which can be used for converts the DC power into AC power at variable frequency and variable voltage .Multilevel inverters come up rapidly because of its high reliability and large capacity with high power and medium voltage applications. The multilevel inverters are the combination of the semiconductor switches, capacitors ,diodes and voltages sources . That is reduces the THD, switching voltages and improved the output waveform it is seems like a sinusoidal waveform.

The main advantages of the multilevel inverters over conventional inverters faces low switching losses at high frequency and it is less affected with the THD , electromagnetic interference and low dv/dt stress . Table- I are shows that the comparision between the conventional inverter and MLI.To solve the high voltage and current stress ,THD ,interference. [1-10]

A multilevel inverter is dc input voltage source it is trying to gives a pure sinusoidal output waveform due to multiple voltage levels. It is used to smooth running of the AC drives motors.

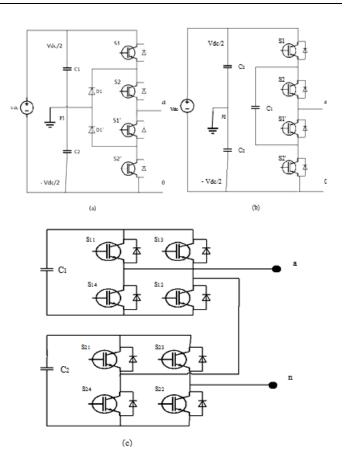

There are three types of main MLI topologies introduced as follows:

- Neutral Point Clamped / Diode Clamped MLI

- Capacitor Clamped / Flying Capacitor MLI

- Cascaded H-Bridge Multilevel Inverter

The topology proposed a diode clamped, capacitor clamped and cascaded inverter which is H bridge .The connection of H-bridge inverter in series this is called a cascaded H-bridge inverter. In the above these topology the first invented topology is diode clamped .The diode clamped topology is consists of input voltage source, diode and semiconductor switches. The diode clamped topology is reduced the voltage stress at the switches.[9,36,40]

TABLE I: Comparison of conventional Inverter and Multilevel Inverter

| SI.<br>No. | Conventional<br>inverter             | Multilevel inverter                     |

|------------|--------------------------------------|-----------------------------------------|

| 1.         | High rate of<br>change of<br>voltage | Low rate of change voltage              |

| 2.         | Switching stress are high            | Switching stress are low                |

| 3.         |                                      | Used for high<br>voltage<br>application |

| 4.         | EMI are more                         | EMI are less                            |

| 5.         | High switching frequency             | Low switching frequency                 |

| 6.         | Low power<br>application             | High power<br>application               |

The comparison of these three topologies the cascaded H-bridge inverter[18] is mostly used because it reduces the voltage stress ,distortion in the input current and low total harmonic distortion .The everything has a limitation beyond its limitation its complexity will be increased and it gives a disadvantages instead of advantages. There is too many topologies are present at this time we want to reduce the total harmonic distortion and increasing the smoothness of the waveform [11-37]. We are observed these topologies .In this paper we are discuss about the topologies merits and demerits. The topological review the paper accentuation on the different types of modulation and optimization techniques [39-49] and reduces the total harmonic distortion.

#### 2. RECENT MULTILEVEL INVERTER TOPOLOGIES

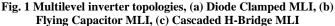

#### A. Active Neutral Point Clamped (ANPC)MLI

A five level ANPC topology[1] shown in fig 2 it is overcome the unbalance power loss distribution .The switching states table are shown the five level of voltages .Auther Eduardo Burguete are used the four auxillary capacitors and one larger capacitor C1 is used in the 5 level ANPC MLI. The working of the capacitor which is used in the ANPC are as:

- (i) It avoids the semiconductor devices in series and reduces the hardware requirements and unbalanced of the voltage.

- (ii) It reduces the overvoltage during the commutation and provides the low inductance path for current. Advantages of auxillary capacitors:

- (i) Voltage blocking are equal and no extra hardware are required and semiconductor which is connected in series are avoided.

- (ii) Reduces the overvoltage during the commutation which provides the low inductance path for current.

Fig. 2 Five level ANPC Topology

#### TABLE II: SWITCHING STATES OF THE NEW 5L-ANPC

| Switching<br>Vectors | Switch State |      |       |      |      |    |    | Output<br>Voltage |      |      |       |   |                          |

|----------------------|--------------|------|-------|------|------|----|----|-------------------|------|------|-------|---|--------------------------|

|                      |              | S1 S | 52 S. | 3 S4 | I S5 | S6 | S7 | S8                | S9 S | 10 S | 11 S1 | 2 | Vo                       |

| V1                   | 1            | 1    | 1     | 1    | 0    | 0  | 0  | 0                 | 0    | 1    | 0     | 1 | + V dc / 2               |

| V2                   | 1            | 1    | 1     | 0    | 1    | 0  | 0  | 0                 | 0    | 1    | 0     | 1 | + V dc / 4               |

| V3                   | 0            | 1    | 1     | 1    | 0    | 0  | 0  | 1                 | 1    | 1    | 0     | 1 | + V dc / 4               |

| V4                   | 0            | 1    | 1     | 0    | 1    | 0  | 0  | 1                 | 1    | 1    | 0     | 1 | 0(+)                     |

| V5                   | 0            | 1    | 0     | 1    | 0    | 1  | 0  | 1                 | 1    | 1    | 1     | 0 | 0(-)                     |

| V6                   | 0            | 1    | 0     | 0    | 1    | 1  | 0  | 1                 | 1    | 1    | 1     | 0 | $-V \operatorname{dc}/4$ |

| V7                   | 0            | 0    | 0     | 1    | 0    | 1  | 1  | 1                 | 1    | 0    | 1     | 0 | $-V \operatorname{dc}/4$ |

| V8                   | 0            | 0    | 0     | 0    | 1    | 1  | 1  | 1                 | 1    | 0    | 1     | 0 | $-V \operatorname{dc}/2$ |

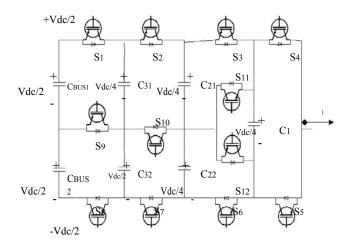

#### B. Auxiliary Switch 5L-CHB MLI

The comparision between the conventional H-bridge[2] topology and modern H-bridge topology are as: The conventional H-bridge topology have auxiliary bi-directional switch to minimize the circuit complexity. The modern H-

bridge topology consists of the modulator , firing control circuit using FPGA. This topology have no requirement of the diodes and capacitors which can be reduces the main power switches .The voltage swing will be observed across the capacitor .The two capacitors are connected in parallel to maintain the operating range limitation.

Fig.3 Diagram of five level H-bridge inverter its output is shown in TABLE III.

circuit of the cross connected multilevel inverter are used for both symmetrical as well as asymmetrical .It is controlling the equal load sharing in a higher level topology.

CCS-MLI topology is used for different switching frequencies and the available literature are concluded the higher switching frequencies .The voltage stress are reduced .Fig 4 are shows the CCS-MLI topology with the DC sources are cross connected.

Fig.3 Auxiliary Switch Cascade H-Bridge Topology

| S1  | S2  | S3  | S4  | S5  | VR    |

|-----|-----|-----|-----|-----|-------|

| ON  | OFF | OFF | ON  | OFF | Vs    |

| OFF | OFF | OFF | ON  | ON  | Vs/2  |

| OFF | OFF | ON  | ON  | OFF | 0     |

| OFF | ON  | OFF | OFF | ON  | -Vs/2 |

| ON  | OFF | OFF | ON  | OFF | -Vs   |

TABLE III: Switching Combinations Required to Generate Five Level Output Voltage Waveform

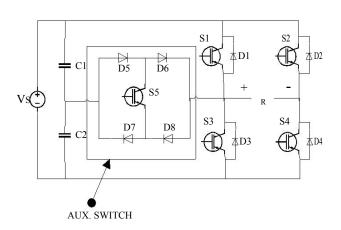

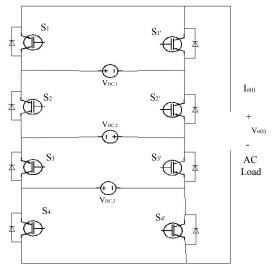

#### C. Cross-Connected Source-Based Multilevel Inverter (CCS-MLI) Topology

A cross connected source multilevel inverter [4] are introduces the connection of the DC sources are in opposite polarity. The opposite polarity of the DC sources are minimizes the component count. In this topology the less active switch counts and the compressed switching losses are less. This topology are also used as level doubling network. It is doubling the level of the output voltage. The generalized

Table IV showing the possible switching combinations, output level and conducting switches.

Fig. 4 CCS- MLI Topology

| State | Output<br>Level | Source<br>combination            | Conducting<br>Switches                                                                                                                      |

|-------|-----------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VDC             | V <sub>DC,1</sub>                | $S_1, S_2', S_3', S_4'$                                                                                                                     |

| 2     | V <sub>DC</sub> | VDC,2                            | $S_1{}', S_2{}', S_3, S_4$                                                                                                                  |

| 3     | VDC             | Vdc,3                            | $S_1, S_2, S_3, S_4'$                                                                                                                       |

| 4     | 2 Vdc           | $V_{DC,1} + V_{DC,2}$            | $S_1, S_2', S_3, S_4$                                                                                                                       |

| 5     | 2 Vdc           | $V_{DC,2} + V_{DC,3}$            | S <sub>1</sub> , S <sub>2</sub> , S <sub>3</sub> , S <sub>4</sub>                                                                           |

| 6     | 3 Vdc           | $V_{DC,1} + V_{DC,2} + V_{DC,3}$ | $S_{1}{}', S_{2}{}', S_{3}, S_{4}{}'$                                                                                                       |

| 7     | 0               | -                                | S <sub>1</sub> , S <sub>2</sub> , S <sub>3</sub> , S <sub>4</sub><br>S <sub>1</sub> ', S <sub>2</sub> ', S <sub>3</sub> ', S <sub>4</sub> ' |

### TABLE IV: Switching combinations for positive voltage levels in CCS-MLI

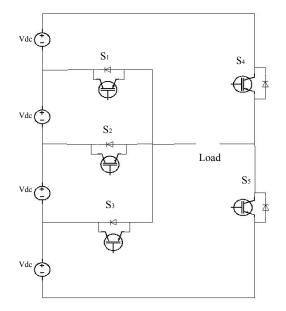

five bidirectional switches .Both are produces the same output voltage but seven level five switches are consists of less number of switches and switching losses are minimized.

Fig. 5 A new Seven Level 5 Switch Topology

Fig. 6 T-Type Inverter Topology

#### D. Seven Level Five Switch MLI Topology

D.Vijay kumar proposed a new seven level MLI [5]with the use of five IGBT switches .The Auther are compare the seven level nine switches topology to the seven level five level bidirectional switch .The seven level nine switches consists of the three DC voltages sources ,five complementary switches and one H-bridge having four switches. While the seven level five switches topology consists of 4 DC voltage sources and In this topology the three positive voltage level and three negative voltage level and one is zero. which is shown in TABLE V.

| <b>TABLE V: Switching</b> | Scheme fo | or Seven Level | 5Switch T | Topology |

|---------------------------|-----------|----------------|-----------|----------|

|---------------------------|-----------|----------------|-----------|----------|

| Sl.<br>No | S1  | S2  | S3  | S4  | S5  | Output<br>Voltage |

|-----------|-----|-----|-----|-----|-----|-------------------|

| 1         | OFF | OFF | ON  | OFF | ON  | +Vdc              |

| 2         | OFF | ON  | OFF | OFF | ON  | +2 Vdc            |

| 3         | ON  | OFF | OFF | OFF | ON  | +3 Vdc            |

| 4         | OFF | OFF | OFF | OFF | OFF | 0                 |

| 5         | ON  | OFF | OFF | ON  | OFF | - Vdc             |

| 6         | OFF | ON  | OFF | ON  | OFF | -2 Vdc            |

| 7         | OFF | OFF | ON  | ON  | OFF | -3 Vdc            |

The table VI shows the different level of voltage and it is not possible the equal load sharing.

TABLE VI: Valid Switching States for T-Type Inverter

| State | Output Voltage             | Switches in ON |

|-------|----------------------------|----------------|

|       |                            | state          |

| 1     | - Vdc,1                    | S1,Q4          |

| 2     | Vdc,4                      | \$3,Q3         |

| 3     | -(Vdc,1+Vdc,2)             | S2,Q4          |

| 4     | Vdc,3+Vdc,4                | S2,Q3          |

| 5     | -(Vdc,1+Vdc,2+Vdc,3)       | S3,Q4          |

| 6     | Vdc,2+Vdc,3+Vdc,4          | S1,Q3          |

| 7     | -(Vdc,1+Vdc,2+Vdc,3+Vdc,4) | Q1,Q4          |

| 8     | Vdc,1+Vdc,2+Vdc,3+Vdc,4    | Q2,Q3          |

| 9     | 0                          | Q1,Q3          |

| 10    | 0                          | Q2,Q4          |

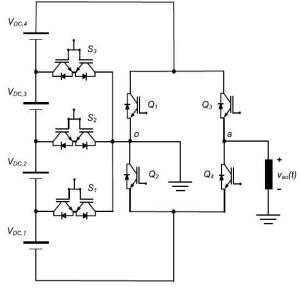

#### E. T-Type MLI Topology

Victor guzman proposed a new MLI which is called as T-Type multilevel inverter topology[6]. The T-Type topology is a five level inverter which is consist of the four input voltage sources three bidirectional switches  $Sj \{j = 1, 2, 3\}$

The bidirectional switches are conducting both the direction of the current .The four switches are unidirectional which is conducting one direction of the current.

The T-Type multilevel inverter topology are symmetric. It is not possible to synthesize the switching pattern combination of the input voltage levels at the output terminals. It takes time only a change in the polarity .The switching pattern are shown in table VI.

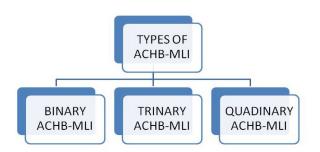

#### F. Asymmetric Cascaded H-Bridge MLI(ACHB-MLI)

E. Babaci proposed the asymmetrical cascaded H-bridge MLI[30] has a unequal magnitude of the DC voltage sources. In this topology the two modules are uses with the different magnitude of the DC voltage sources. This topology are divided into three types according to the magnitude of the DC voltage .

The ACHB-MLI are reduces the extra clamping diodes or capacitors are balancing the DC voltage in other topology in this topology we can reduces the capacitors.

#### 1. Binary ACHB-MLI

In the binary modules the two values of the DC voltage sources are  $V_{dc}$  and  $2V_{dc}$ . The output voltage levels are as:

$$Vn = 2^n$$

,  $n = 1, 2, 3, ...$

n = the H-Bridge module count.

2. Trinary ACHB-MLI

In Trinary modules the DC voltages are  $V_{dc}$  and  $3V_{dc}$  are used.

The output voltage levels are as:

$$Vn = 3^n$$

,  $n = 1, 2, 3, ...$

3. Quadinary ACHB-MLI

In the Quadinary modules the DC voltages are  $V_{dc}$  and  $4V_{dc}$  are used. The output voltage levels are as:

$$\sqrt{n} = 4^n$$

,  $n = 1, 2, 3, ...$

## 3. MODULATION AND OPTIMIZATION TECHNIQUES

There is different types of modulation are to control the output voltage[39-45]. The average voltage are found at the output this is control by the devices. The best modulation technique is pulse width modulation. In the pulse width modulation the variation of width of pulse this is called as duty cycle. The different types of the PWM techniques are used to reduced the harmonics and increases the smoothness of the waveform. The different types of PWM are as follows:

#### A. Single Pulse Width Modulation

A single gate pulse per half cycle is controlled the output voltage.

#### B. Multiple Pulse Width Modulation

The ramp signal is compared with the DC voltage .In this technique the multiple gate pulses per half cycle.

#### C. Sinusoidal Pulse Width Modulation

In this technique the comparision between the two signal are is sinusoidal wave and another is triangular carrier signal. This technique is used to suppressed the higher level of harmonics .The output voltage waveform are in order of n and n+2.

#### n = fc/fm

f<sub>c</sub>=carrier frequency

f<sub>m</sub>=modulating signal frequency

In SPWM technique the controlling of the output waveform by the change in the modulation index.

| Table VII : MLI Advantages and Disadvantages on Comparision |

|-------------------------------------------------------------|

| Basis                                                       |

| Topology          | Advantages           | Disadvantages       |

|-------------------|----------------------|---------------------|

| Active Neutral    | Control of over      | The number of       |

| Point Clamped     | voltage and reduces  | switches are        |

|                   | the over voltage     | increases           |

| Auxiliary Switch  | Number of switches   | Extra circuit is    |

| 5L-CHB            | are less             | required            |

| Cross –connected  | Voltage stress are   | Number of switches  |

| source based      | reduced and having   | are rises gradually |

| inverter          | a equal load sharing | for asymmetrical    |

|                   |                      | topology            |

| Seven level five  | Harmonic             | Not used for higher |

| switch MLI        | distortion are less  | level               |

| T-Type MLI        | Device count are     | Equal load sharing  |

|                   | less                 | is not possible     |

| Asymmetric        | The waveform of      | Unequal voltage     |

| cascaded H-bridge | the output voltage   | stress              |

| MLI               | is look like         |                     |

|                   | sinusoidal           |                     |

#### 4. CONCLUSION

Table VII are shows that the advantages and disadvantages of the various types of topology. An ANPC-MLI topology is reduces the overvoltage .Auxiliary switch CHB-MLI is reduced the number of switch to required in the 5 level output voltage .The seven level 5 switches are reduces the switching losses .CCS-MLI topology are useful for equal load sharing.

#### REFERENCES

- Eduardo Burguete and Mikel Zabaleta, "A New Five-Level Active Neutral-Point-Clamped Converter With Reduced Overvoltages", IEEE Transactions On Industrial Electronics, Vol. 63, No. 11, 2016, pp. 7175-7183.

- [2] Gerardo Ceglia, Víctor Guzmán, Carlos Sánchez, Fernando Ibáñez and

María I. Giménez, "A New Simplified Multilevel Inverter DC-ACPCORVETSTON", IEEE Transactions On Power Electronics, Vol.

- 21, No. 5, 2006, pp.1311-1319.

- [3] R. S. Alishah, S. H. Hosseini, E. Babaei, and M. Sabahi, "A new general multilevel converter topology based on cascaded connection of sub-multilevel units with reduced switching components, dc sources, and blocked voltage by switches," *IEEE Trans. Ind. Electron.*, vol. 63, no. 11, 2016, pp. 7157– 7164.

- [4] Krishna Kumar Gupta, Shailendra Jain, "Comprehensive Review Of A Recently Proposed Multilevel Inverter", IET Power Electron., 2014, Vol. 7, Iss. 3, pp. 467–479.

- [5] S. Umashankar, T. S. Sreedevi, V. G. Nithya, and D. Vijayakumar, "A New 7-Level Symmetric Multilevel Inverter with Minimum Number of Switches", ISRN Electronics Volume 2013, pp.1-9.

- [6] G. Ceglia, V. Guzman, C. Sanchez, F. Ibanez, J.Walter, and M. I. Gimenez, "A new simplified multilevel inverter topology for DC-AC conversion," IEEE Trans. Power Electron., vol. 21, no. 5, 2006, pp. 1311–1319.

- [7] L. Liu, H. Li, S.-H. Hwang, and J.-M. Kim, "An energyefficient motor drive with autonomous power regenerative control system based on cascaded multilevel inverters and segmented energy storage," *IEEE Trans. Ind. Appl.*, vol. 49, no. 1, 2016, pp. 178–188.

- [8] M. S. A. Dahidah, G. Konstantinou, and V. G. Agelidis, "A review of multilevel selective harmonic elimination PWM: Formulations, solving algorithms, implementation and applications," *IEEE Trans. Power Electron.*, vol. 30, no. 8, 2015, pp. 4091–4106.

- [9] Arif Al-Judi, Edwin Nowicki, "Cascading Of Diode Bypassed Transistor-Voltage-Source Units In Multilevel Inverters", Univ. Of Calgary, Canada, IET Power Electron., 2013, Vol. 6, Iss. 3, pp.

Calgary, Canada, IE1 Power Electron., 2013, Vol. 6, Iss. 3, pp. 554–560.

[10] Krishna Kumar Gupta, Alekh Ranjan, Pallavee Bhatnagar, "Multilevel Inverter Topologies with reduced device count: A Review", IEEE

Transactions On Power Electronics, VOL. 31, NO. 1, 2016,

pp.135-151.

- [11] G. Buticchi, D. Barater, E. Lorenzani, C. Concari, and G. Franceschini, "A nine-level grid-connected converter topology for single-phasetransformerless PV systems," *IEEE Trans. Ind. Electron.*, vol. 61, no. 8, Aug. 2014, pp. 3951–3960.

- [12] R. S. Alishah, D. Nazarpour, S. H. Hosseini, and M. Sabahi, "Reduction of power electronic elements in multilevel converters using a new cascade structure," *IEEE Trans. Ind. Electron.*, vol. 62, no. 1, Jan. 2015, pp. 256–267.

- [13] I. Abdalla, J. Corda, and L. Zhang, "Multilevel DC-link inverter and control algorithm to overcome the PV partial shading," *IEEE Trans. Power Electron.*, vol. 28, no. 1, 2013, pp. 14–18.

- [14] R. S. Alishah, S. D. Nazarpour, H. Hosseini, and M. Sabahi, "New hybrid structure for multilevel inverter with fewer number of components for high-voltage levels" *IET Power Electron.*, vol. 7, no. 1, 2014, pp. 96–104.

- [15] E. Babaei, M. F. Kangarlu, and M. Sabahi, "Extended multilevel converters: An attempt to reduce the number of independent dc voltage sources in cascaded multilevel converters," *IET Power Electron.*, vol. 7, no. 1, 2014 pp. 157–166.

- [16] K. K. Gupta and S. Jain, "Topology for multilevel inverters to attain maximum number of levels from given DC sources" *IET Power Electron.*, vol. 5, no. 4, 2013, pp. 435–446.

- [17] E. Babaei and S. H. Hosseini, "New cascaded multilevel inverter topology with minimum number of switches," *J. Energy Convers. Manage.*, vol. 50, no. 11, 2009, pp. 2761–2767.

- [18] M. F. Kangarlu and E. Babaei, "A generalized cascaded multilevel inverter using series connection of submultilevel inverters," *IEEE Trans. Power Electron.*, vol. 28, no. 2, 2013, pp. 625–636.

- [19] K. K. Gupta, A. Ranjan, P. Bhatnagar, L. K. Sahu, and S. Jain,

"Multilevel inverter topologies with reduced device count: A review,"

IEEE Trans. Power Electron., vol. 31, no. 1, 2016, pp. 135-151.

[20] B. Xiao, F. Filho, and L. M. Tolbert, "Single-phase cascaded Hbridge multilevel inverter with non active power compensation for grid-connected photovoltaic generators," in Proc. IEEE Energy Convers.

Congr. Expo., Sep. 17-22, 2011, pp. 2733-2737.

- [21] F. Filho, Y. Cao, and L. M. Tolbert, "11-Level cascaded Hbridge grid-tied inverter interface with solar panels," inProc. IEEE App. Power Electron. Conf., Feb. 21–25, 2010, pp. 968–972.

- [22] J. Ebrahimi, E. Babaei, and G. B. Gharehpetian, "A new multilevel converter topology with reduced number of power electronic components," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, 2015, pp. 655–667.

- [23] J. Ebrahimi, E. Babaei, and G. B. Gharehpetian, "A new multilevel converter topology with reduced number of power electronic components," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, , Feb. 2012, pp. 655–667.

- [24] R. Feldman *et al.*, "A hybrid modular multilevel voltage source converter for HVDC power transmission," *IEEE Trans. Ind. Appl.*, vol. 49, no. 4, 2013, pp. 1577–1588.

- [25] M. F. Kangarlu and E. Babaei, "Cross-switched multilevel inverter: An innovative topology," *IET Power Electron.*, vol. 6, no. 4, 2013, pp. 642–651.

- [26] M.A. Perez, P. Cortes, and J. Rodriguez, "Predictive control algorithm technique for multilevel asymmetric cascaded H-

bridge inverters," *IEEE Trans. Ind. Electron.*, vol. 55, no. 12, pp. 4354–4361, Dec. 2008.

- [27] E. Villanueva, P. Correa, J. Rodriguez, and M. Pacas, "Control of a single phase cascaded H-bridge multilevel inverter for gridconnected photovoltaic systems," *IEEE Trans. Ind. Electron.*, vol. 56, no. 11, Nov. 2009, pp. 4399–4406.

- [28] F. Z. Peng, W. Qian, and D. Cao, "Recent advances in multilevel converter/ inverter topologies and applications," in *Proc. Int. Power Electron. Conf.*, 2010, pp. 492–501.

- [29] R. Stala, "Application of balancing circuit for DC-link voltages balance in a single-phase diode-clamped inverter with two threelevel legs," *IEEE Trans. Ind. Electron.*, vol. 58, no. 9, 2011, pp. 4185–4195.

- [30] E. Babaei and M. S. Moeinian, "Asymmetric cascaded multilevel inverter with charge balance control of a low resolution symmetric subsystem," *J. Energy Convers. Manage.*, vol. 51, no. 11, 2010, pp. ,2272–2278.

- [31] A. Mokhberdoran and A. Ajami, "Symmetric and asymmetric design and implementation of new cascaded multilevel inverter topology," *IEEE Trans. Power Electron.*, vol. 29, no. 12, 2014, pp. 6712–6724.

- [32] E. Villanueva, P. Correa, J. Rodriguez, and M. Pacas, "Control of a single phase cascaded H-bridge multilevel inverter for grid connected photovoltaic systems", IEEE Trans. Ind. Electron., vol. 56, no. 11, 2009, pp. 4399–440.

- [33] S. Vazquez, J. I. Leon, J. M. Carrasco, L. G. Franquelo, E. Galvan, M. Reyes, J. A. Sanchez, and E. Dominguez, "Analysis of the power balance in the cells of a multilevel cascaded H-bridge converter," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2287–2296, Jul. 2010.

- [34] S. Rivera, S. Kouro, B. Wu, J. I. Leon, J. Rodriguez, and L. G. Franquelo, "Cascaded H-bridge multilevel converter multistring topology for large scale photovoltaic systems," inProc. IEEE Int. Symp. Ind. Electron., Jun. 27–30, 2011, pp. 27–30.

- [35] S.-J. Park, F.-S. Kang, M. H. Lee, and C.-U Kim, "A new single-phase five-level PWM inverter employing a dead beat control scheme," *IEEE Trans. Power Electron.*, vol. 18, no. 3, May 2003, pp. 831–843.

- [36] M. M. Renge and H. M. Suryawanshi, "Five-level diode clamped inverter to eliminate common mode voltage and reduce dv/dt in medium voltage rating induction motor drives," *IEEE Trans. Power Electron.*, vol. 23, no. 4, pp. 1598–1607, Jul. 2008.

- [37] H. Abu-Rub, J. Holtz, J. Rodriguez, and G. Baoming, "Medium voltage multilevel converters state of the art, challenges and requirements in industrial applications," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, 2010, pp. 2581–2596.

- [38] P. Lezana, R. Aguilera, and D. E. Quevedo, "Model predictive control of an asymmetric flying capacitor converter," *IEEE Trans. Ind. Electron.*, vol. 56, no. 6, pp. 1839–1846, Jun. 2009.

- [39] C. Feng, J. Liang, and V. G. Agelidis, "Modified phase-shifted PWM control for flying capacitor multilevel converters," *IEEE Trans. Power Electron.*, vol. 22, no. 1, pp. 178–185, Jan. 2007.

- [40] E. Najafi and A. H. M. Yatim, "Design and implementation of a new multilevel inverter topology," *IEEE Trans. Ind. Electron.*, vol. 59, no. 11, pp. 4148–4154, Nov. 2012.

- [41] M. Odavic, V. Biagini, M. Sumner, P. Zanchetta, and M. Degano, "Low carrier-fundamental frequency ratio PWM for multilevel active shunt power filters for aerospace applications,"

IEEE Trans. Ind. Appl., vol. 49, no. 1, 2013, pp. 159-167.

- [42] R. Rabinovici, D. Baimel, J. Tomasik, and A. Zuckerberger, "Series space vector modulation for multi-level cascaded Hbridge inverters," *IET Power Electron.*, vol. 3, no. 6, pp. 843– 857, Nov. 2010.

- [43] J. Mei, B. Xiao, K. Shen, L. M. Tolbert, and J. Y. Zheng, "Modular multilevel inverter with new modulation method and its application to photovoltaic grid-connected generator," *IEEE Trans. Power Electron.*, vol. 28, no. 11, 2013, pp. 5063–5073.

- [44] P. Palanivel ,S.S. Dash, "Analysis of THD and output voltage performance for cascaded multilevel inverter using carrier pulse width modulation techniques", SRM University, Chennai, India, IET Power Electron., 2011, Vol. 4, Iss. 8, pp. 951–958

- [45] F. Zhang and Y. Yan, "Selective harmonic elimination PWM control scheme on a three-phase four-leg voltage source inverter," *Power Electronics, IEEE Transactions on*, vol. 24, no. 7, 2009, pp. 1682–1689.

- [46] H. Taghizadeh and M. T. Hagh, "Harmonic Elimination of Cascade

Multilevel Inverters with Nonequal DC sources Using Particle Swarm

Optimization", *IEEE Trans. on Industrial Electronics*, 2010, Vol. 57, No. 11.

- [47] G. T. Son, Y. H. Chung, S. T. Baek, H. J. Kim, T. S. Nam, K. Hur and J.

W. Park, "Improved PDPWM for Minimizing Harmonics of Multilevel Inverter Using Gradient Optimization", in *Proc. IEEE PES. Gen. Meeting Conf. Expo.*, 2014, pp. 1-5.

- [48] V. K. Gupta and R. Mahanty, "Optimized Switching Scheme of Cascaded H- Bridge Multilevel Inverter Using PSO", *International Journal of Electrical Power and Energy Systems*, Vol. 64, 2015, pp. 699 – 707.

- [49] J. Yuan, J. Pan, W. Fei, C. Cai, Y. Chen, and B. Chen, "An immune algorithm- based space-vector PWM control strategy in a three-phase inverter," *Industrial Electronics, IEEE Transactions on*, vol. 60, no. 5, 2013, pp. 2084–2093